在半导体产业链中,测试环节是确保芯片性能、良率与长期稳定性的关键屏障。而作为承载芯片进行功能验证与参数筛选的核心载体——半导体测试板(Tester PCB / Load Board),其制造质量直接决定了测试结果的准确性与重复性。在这其中,高精度SMT贴片技术扮演着“精密守护者”的角色,为测试板的信号完整性、热稳定性与机械可靠性提供坚实保障。本文将分享SMT贴片工艺如何赋能半导体测试板制造,助力客户实现高效、可信的芯片验证流程。

一、半导体测试板的特殊性:为何对SMT提出极致要求?

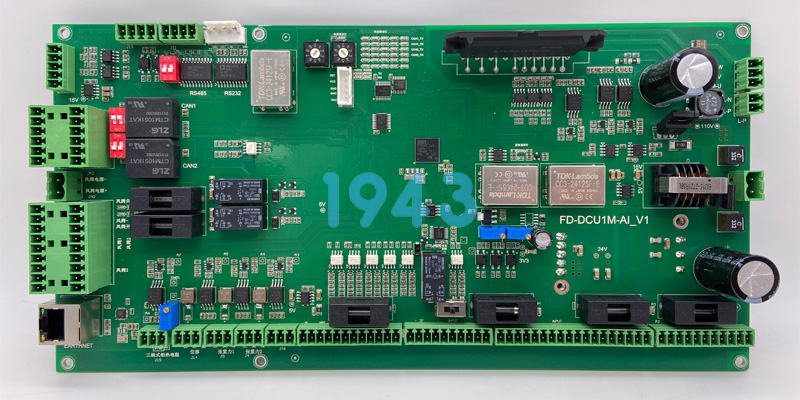

半导体测试板不同于普通PCB,它需在高频、高速、高密度条件下精准传递微弱电信号,同时承受反复插拔、高温老化及大电流冲击。其典型特征包括:

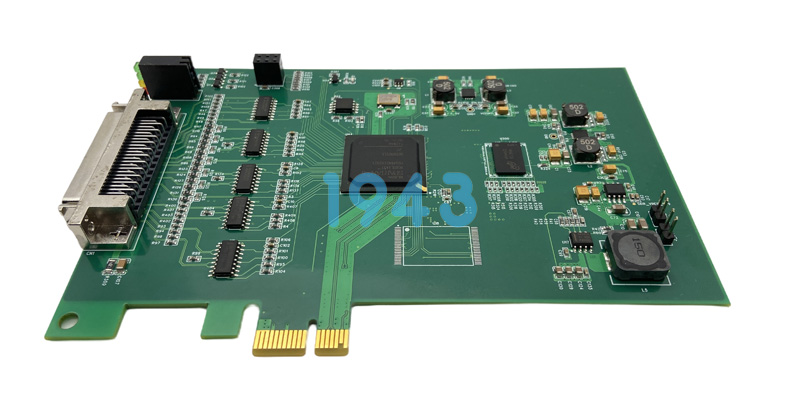

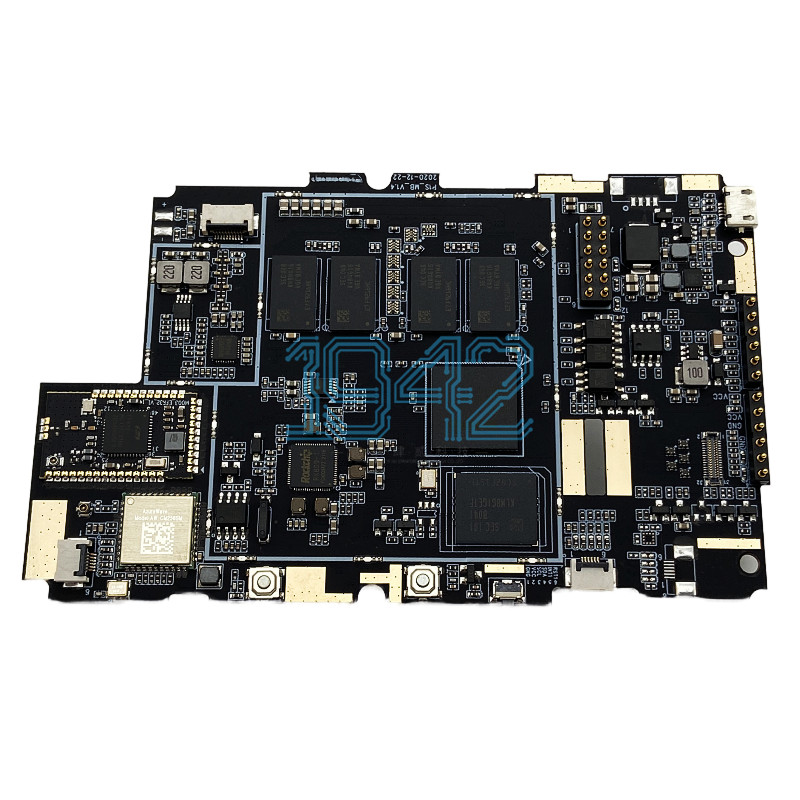

- 超高布线密度:常采用8~20层甚至更多叠层结构,线宽/线距可小至50μm;

- 严苛阻抗控制:差分对阻抗公差通常要求±5%以内,以保障信号完整性;

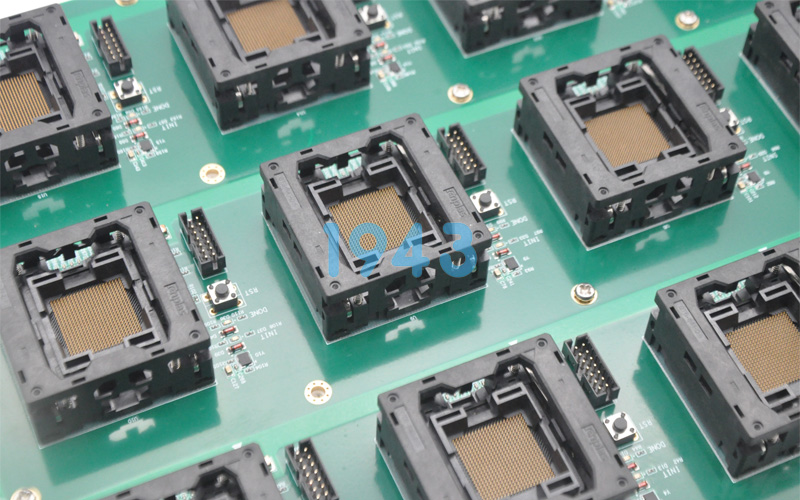

- 精密连接器集成:如Socket、探针卡接口等,对焊盘共面性与位置精度要求达±25μm;

- 长期重复使用:单块测试板可能经历数千次测试循环,焊点必须具备卓越抗疲劳能力。

这些特性决定了其SMT贴片过程不能依赖常规工艺,而需一套高度专业化、数据驱动的制造体系。

二、SMT贴片技术如何守护测试板可靠性?

1. 微米级贴装精度,确保信号路径一致性

测试板上常集成大量0201无源器件及QFN、BGA封装IC。专业SMT设备通过高分辨率激光视觉系统,结合动态补偿算法,实现±30μm的贴装精度,避免因元件偏移导致的寄生电感/电容变化,从而维持高频信号传输稳定性。

2. 定制化锡膏印刷与回流工艺

针对细间距焊盘与密集通孔,采用激光钢网开孔+3D SPI闭环控制,确保锡膏体积一致性;回流焊曲线则根据板材Tg值、元器件热敏感度动态优化,防止热应力引发微裂或空洞,尤其保障BGA底部焊点的完整性。

3. 焊点可靠性强化措施

- 对关键信号路径焊点实施选择性底部填充(Underfill);

- 采用低空洞率无铅焊料,并通过X-Ray检测焊球空洞率(控制在<15%);

- 所有连接器区域执行AOI+人工复判双重检验,杜绝虚焊、立碑等缺陷。

4. 洁净度与ESD全流程管控

测试板对离子污染极为敏感。1943科技在SMT车间实施Class 10,000级洁净管理,所有操作人员佩戴双回路静电手环,物料周转使用防静电容器,确保表面绝缘电阻(SIR)符合IPC-TM-650标准。

三、DFM协同:从设计源头提升可制造性

专业SMT贴片厂的价值不仅在于“做得准”,更在于“提前防错”。在半导体测试板项目启动阶段,1943科技工程团队会深度参与DFM(可制造性设计)评审,重点关注:

- 基准点(Fiducial Mark)是否满足高精度贴片机识别需求;

- 焊盘设计是否适配钢网开孔与回流焊润湿特性;

- 大面积铜箔是否合理分割,避免热不平衡导致板翘;

- 测试点布局是否避开高元件阴影区,便于后续功能验证。

通过早期介入,可减少70%以上的潜在制造风险,缩短NPI周期。

四、1943科技:专注高可靠性测试板SMT制造

作为技术驱动型SMT贴片服务商,1943科技已建立面向半导体测试应用的专项工艺平台:

- 配备支持0.3mm CSP贴装的高精度贴片系统;

- 拥有独立的老化与热循环测试区,可模拟实际使用环境;

- 提供从Gerber解析、钢网设计、首件确认到批量追溯的全链路服务;

- 所有测试板产品均附带工艺履历报告,包含SPI/AOI/X-Ray数据摘要。

我们深知,一块测试板的失效,可能导致整批芯片误判。因此,我们以“零容忍”态度对待每一个焊点、每一微米偏差。

五、致芯片设计与封测工程师的建议

若您正在开发新一代测试板,建议在设计阶段即考虑以下SMT友好性要素:

- 预留足够光学识别区域,避免密集走线遮挡基准点;

- 关键高速信号路径尽量避开过孔密集区;

- 在连接器周边增加定位孔与加强筋,提升机械强度;

- 明确标注高可靠性区域,便于SMT厂配置专属工艺参数。

结语

在半导体产业向先进制程不断演进的今天,测试板已从“辅助工具”升级为“质量守门人”。而SMT贴片技术,正是这道防线最精密的基石。1943科技将持续深耕高可靠性PCBA制造,以毫米级的工艺控制,守护每一颗芯片的真实性能。如需获取半导体测试板SMT工艺指南或定制化制造方案,欢迎联系我们的技术团队,开启高精度合作之旅。

2024-04-26

2024-04-26